SERVICES

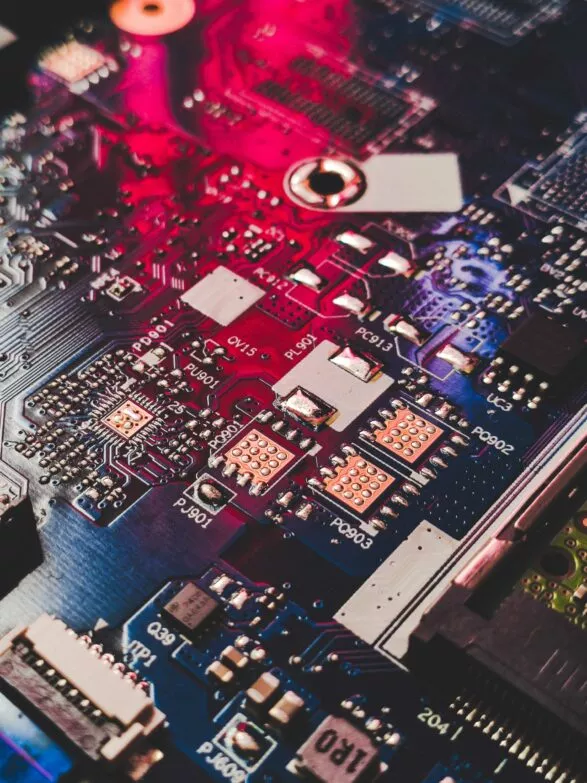

PCBA Testability Analysis

Ensuring your design is optimized for manufacturing and testing

From design to production

ASTER provides professional testability analysis service by employing the TestWay Express software specifically designed for DfT and test coverage analysis to:

- Verify the testability of your design

- Determine cost efficient test strategies while ensuring maximum coverage

- Understand the actual test coverage provided by the various test programs

Our team of test engineers will conduct comprehensive checks and simulations, ensuring that your design is optimized for manufacturing and testing.

DfT analysis

Our test engineers will rely on TestWay Express to perform electrical rules checks, for design and testability violations and evaluate the accessibility for test probes.

- Design rules to verify conformance restrictions imposed by certain technologies i.e. open-drain, noise immunity, etc.

- Boundary-scan rules to verify chain integrity, compliance, presence of bypass resistors, flash programming optimization, identifying clusters and bus terminations, etc.

- Testability violations to insure initialization and test partitioning, for example; chip select, output enable, test pins, etc.

- Mechanical board analysis (mDfT) to place test probes and confirm net access is not compromised by solder mask, etc.

Test strategy analysis

Our test engineers will employ TestWay Express to simulate various test strategies, aiming to achieve the highest test coverage.

- Estimate coverage for SPI, AOI, BST, X-Ray, ICT and Flying probe

- Optimize test points to minimize fixture costs while maintaining full board coverage

- Measure real coverage to verify test program performance